|

SimAVR

AVR Simulator

|

|

SimAVR

AVR Simulator

|

Generic BitBang Module of simavr AVR simulator. More...

Data Structures | |

| struct | avr_bitbang_t |

| SPI Module initialization and state structure. More... | |

Typedefs | |

| typedef struct avr_bitbang_t | avr_bitbang_t |

| SPI Module initialization and state structure. More... | |

Functions | |

| void | avr_bitbang_reset (avr_t *avr, avr_bitbang_t *p) |

| reset bitbang sub-module More... | |

| void | avr_bitbang_start (avr_bitbang_t *p) |

| start bitbang transfer More... | |

| void | avr_bitbang_stop (avr_bitbang_t *p) |

| stop bitbang transfer More... | |

Generic BitBang Module of simavr AVR simulator.

| typedef struct avr_bitbang_t avr_bitbang_t |

SPI Module initialization and state structure.

| void avr_bitbang_reset | ( | avr_t * | avr, |

| avr_bitbang_t * | p | ||

| ) |

reset bitbang sub-module

| avr | avr attached to |

| p | bitbang structure |

| void avr_bitbang_start | ( | avr_bitbang_t * | p | ) |

start bitbang transfer

buffers should be written / cleared in advanced timers and interrupts are connected

| p | bitbang structure |

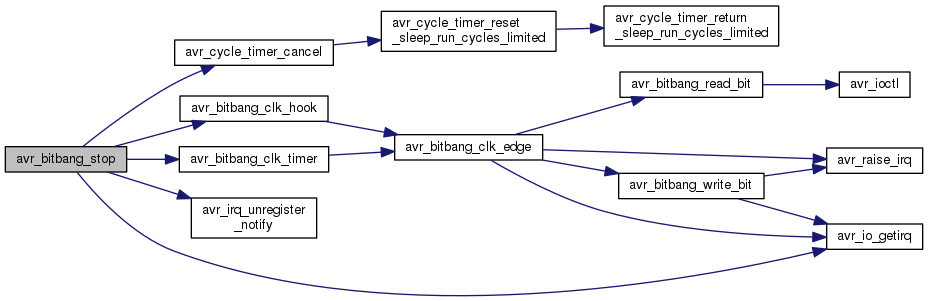

| void avr_bitbang_stop | ( | avr_bitbang_t * | p | ) |

stop bitbang transfer

timers and interrupts are disabled

| p | bitbang structure |